SIEMENS SIMATIC S7 + WINCC

Programming Languages

The operation of the PLC is based on a set of instructions known as a program, developed to meet the user's routines. The signals from sensors or transducers coupled to the machine or equipment are applied to the controller inputs. In each cycle, called a scan, there are three steps:

• Input step – All signals from the external environment and applied to the inputs are read and transferred to an area of the PLC internal memory unit, called the input image table.

• Program step - The program is executed, using the signals acquired during the input stage and deciding what the values of the digital and analog output signals will be. These values are stored in a memory region called the output image. During program execution, the output signals are not changed unless high priority inputs are activated. Such inputs are used for emergencies, which cannot wait for the scan to finish. In this case, we interrupt the work of the PLC, running a program that answers the interruption. After completing the interruption, we return to the main program.

• Output step – All output values established by the program and stored in the output image are applied to the output modules.

After the three steps are complete, the scan cycle is restarted, with the entry step (cyclic operation). In some situations, for example, when using PID controllers, it is necessary to make signal acquisitions (input step) at fixed intervals. In this case, when the exit step is finished, the PLC is waiting for the predefined time to restart the scan (periodic operation).

To perform the control task, the PLC processor simply executes the instructions script contained in the programming table that the user has created step by step. The execution process approximately follows the routine shown in the flowchart below.

Step 7 supports the following programming languages for creating user programs:

Function Block Diagram (FBD)

Ladder Diagram (LAD)

Statement List (STL)

Ladder Programming Language (LAD)

LAD is a graphical programming language. Its representation is based on circuit diagrams. The program is developed in one or more networks. A network contains a power rail on the left. The binary signals are arranged in the form of contact on the networks. A serial arrangement of the elements in a network creates a serial connection; simultaneous branch arrangements create a parallel connection. Complex functions are represented in boxes.

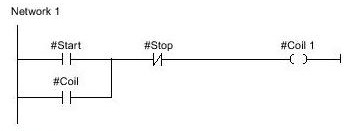

LAD network example

The image below shows a LAD network with two normally open contacts, a normally closed contact and a coil (coil).

LAD elements

A LAD program consists of separate elements that are arranged in series or parallel on the network's power rail. Most elements of the program must be tagged.

The structure of a ladder diagram corresponds to a series of relay switches.

The left power rail on the left is located on the left side in the LD editor. It corresponds to the phase (L ladder) of a connection. In LD programming, as well as electrical connections, only LD objects that are connected to the power supply are processed. The right power rail corresponds to the neutral wire. All coils are directly or indirectly connected to this rail, creating a current flow.

Elements of a LAD network

1 – Power rail

Each LAD network consists of a power rail that contains at least one rung. A network can be extended with the addition of new rungs. Branchs are used for parallel programming on the rungs.

2 – Rung

3 – Branch

4 – Contact

Contacts are used to create or interrupt a connection for current flow between two elements. The chain runs from left to right. Contacts can be used to extract the status of the signal or the value of an operand and control it depending on the result of the current flow.

The following types of contacts are allowed in an LAD program:

Contact types

Normally open

In the case of normally open contacts, the status of the link on the left is transferred to the link on the right if the Boolean parameter (indicated with xxx) is ON. If not, the link status on the right will be OFF.

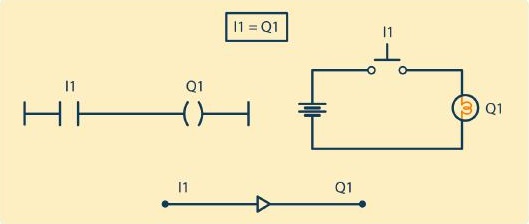

The image below shows the NO contact instruction in ladder, as well as the electrical circuit and the corresponding digital logic.

Note that in the Contact NO instruction, the state of the digital output is identical to that of the digital input. Thus, when I1 is at a high level, output Q1 will be activated; and, when I1 is at a low level, output Q1 will be disabled.

Normalmente fechado

In the case of normally closed contacts, the status of the link on the left is transferred to the link on the right if the Boolean parameter (indicated with xxx) is OFF. If not, the link status on the right will be OFF.

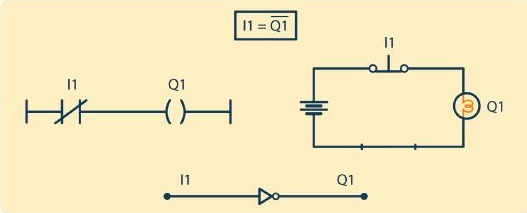

The image below shows the NO contact instruction in Ladder, as well as the electrical circuit and the corresponding digital logic.

Note that in the NC Contact instruction, the state of the digital output is reversed from that of the digital input. Thus, when I1 is at a high level, output Q1 will be disabled; and, when I1 is low, output Q1 will be activated.

5 – Coil

A coil is an LD element that transfers the status of the horizontal link on the left, without modifying it, to the horizontal link on the right. The status is saved in the respective boolean parameter.

Coils types

Coil

With coils, the status of the link on the left is transferred to the boolean parameter (indicated by xxx) and to the link on the right.

Negated Coil

With negated coil, the status of the link on the left side is copied to the link on the right side. The inverted status of the link on the left is copied to the Boolean parameter (indicated by xxx). If the left link is OFF, then the right link will also be OFF and the Boolean parameter will be ON.

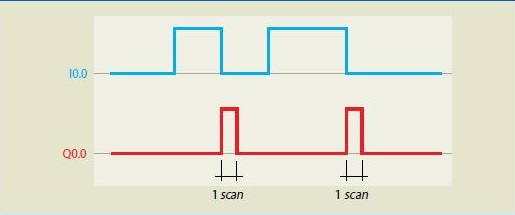

Coil for positive transition detection

With coils for positive transition detection, the status of the link on the left is copied to the link on the right. The parameter of type EBOOL (indicated by xxx) is 1 for a program cycle, if the transition of the left link from 0 to 1 is made.

The state diagram of the normally open contact input (I0.0) and the coil output for positive transition detection (Q0.0) demonstrates the application of this instruction. Note that when the input (I0.0) is activated, that is, on the transition from logic level “0” to “1”, a pulse with a duration of 1 scan appears on the output associated with that input. When descending, when going from logical level “1” to “0”, nothing happens at the exit.

Coil for negative transition detection

With coils for positive transition detection, the status of the link on the left is copied to the link on the right. The parameter of type EBOOL (indicated by xxx) is 1 for a program cycle, if the transition of the left link from 1 to 0 is made.

The state diagram of the normally open contact input (I0.0) and the coil output for negative transition detection (Q0.0) demonstrates the application of this instruction. Note that when the input (I0.0) is activated, nothing happens; however, when it is switched off, when switching from logic level "1" to "0", a pulse with a duration of 1 scan appears on the output associated with that input.

Set Coil

With set coils, the status of the link on the left is copied to the link on the right. The boolean parameter (indicated by xxx) receives ON if the left link has an ON status, otherwise it is not changed. The boolean parameter can go to OFF (reset) through the reset coil.

Reset Coil

With reset coils, the status of the link on the left is copied to the link on the right. The boolean parameter (indicated by xxx) receives OFF if the left link has an ON status, otherwise it is not changed. The boolean parameter can go to ON (set) via the set coil.

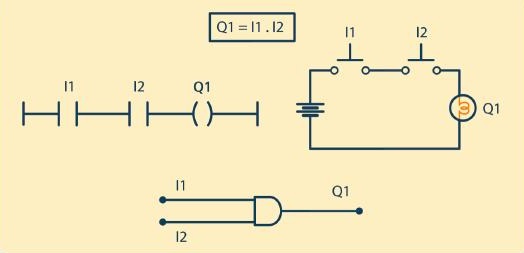

AND: The image shows the E function in Ladder, as well as the electrical circuit and the corresponding digital logic.

Note that in function E, the status of the digital output depends on the combination of the digital inputs. Thus, when I1 and I2 are simultaneously at a high level, output Q1 will be activated; and, when either or both inputs are at low level, output Q1 will be disabled. The image below shows the PLC installation circuit for the program.

OR: The image shows the OR function in Ladder, as well as the electrical circuit and the corresponding digital logic.

Note that, in the OR function, the status of the digital output depends on the combination of the digital inputs. Thus, when I1 or I2, or both, are at a high level, output Q1 will be activated; and, only when I1 and I2 are simultaneously in low level, we will have the output Q1 deactivated.

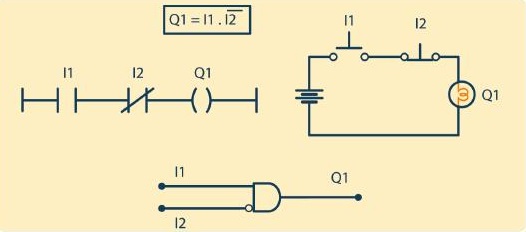

Serial NO-NC Instructions

The image below shows the series NO-NC function in Ladder, as well as the electrical circuit and the corresponding digital logic.

Note that in the serial NO-NC function, the status of the digital output depends on the combination of the digital inputs. Thus, only when I1 is at high and I2 at low level, will we have output Q1 activated. For any other situation, we will have output Q1 deactivated.

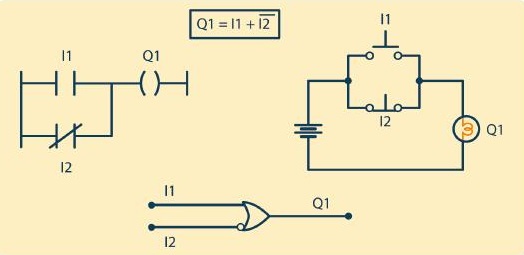

Parallel NO-NC Instructions

The image below shows the parallel NO-NC function in Ladder, as well as the electrical circuit and the corresponding digital logic.

Note that in the parallel NO-NC function, the status of the digital output depends on the combination of the digital inputs. Thus, only when I1 is at a low level and I2 at a high level, will we have output Q1 deactivated. For any other situation, we will have output Q1 activated.

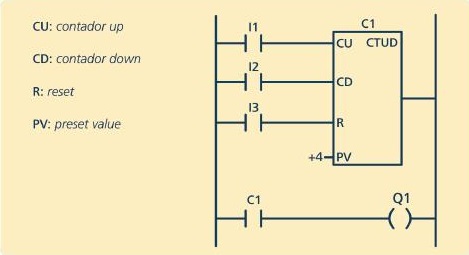

Counters

A counter aims to activate a memory or an output memory after a certain event count. The following image shows the instruction and symbology of the meter, according to IEC 1131-3.

Note that, in the counter instruction, input I1 receives pulses from external keys or sensors, sending to counter C1. In the program, C1 was parameterized for 4 accounts. After C1 receiving 4 pulses (four energies / de-energizations), the NO contact of the C1 counter closes, activating the output Q1.

The counter can be increasing, decreasing or even ascending descending (up/down). For the last purpose, the counter block is composed too much of an entry that will count down, according to the following image.

It is observed that I1 makes the account growing, I2 the account and I3 triggers the reset. The following image shows the diagram of counter times up/down.

After completing the counting cycle (4 counts), Q1 is activated, regardless of the state of I1. The output Q1 can be deactivated by resetting counter C1.

Timers

This function is intended to activate or switch off a memory or an output according to a programmed time.

It is important to note that the timers have several modes of operation, such as delay in energization, delay in de-energization, memorizable delays, etc.

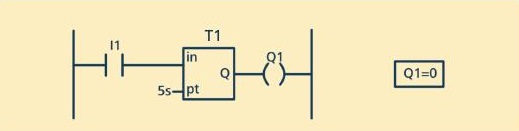

The following image shows the timer instruction with its respective symbology, according to IEC 1131-3.

Next, the most basic timing modes will be displayed.

a) Delay in energization

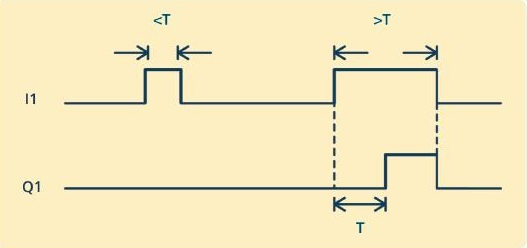

When the timer is set for delay in (Timer On), the Q1 output will be activated a certain time after the I1 input is set high, it is turned off for 5 seconds. When I1 input is at a high level, it activates T1 timer element (parameterized in the program to 5s). After 5 seconds, the timer contact is closed by activating Q1 output.

In the image below we have the time diagram of the timer with delay energization.

Note that if the high level time of input I1 is shorter than the timer setting, Q1 output will not be triggered. Thus, for Q1 output to be triggered, it is necessary that the I1 input remains at a higher level for longer than parameterized T.

It notes, moreover, that in the delayed mode of energization, when you enterI1 there is a level drop, Q1 output turns off immediately.

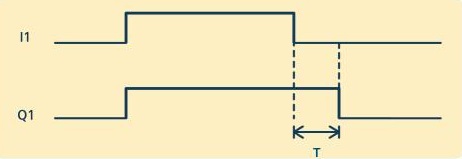

b) Delay in de-energization

When the timer is set to Timer Off, Q1 output will activate immediately when input I1 is at a high level, however, when input I1 is level, Q1 output will remain triggered for time. parameterized T. In the image below we have the timer time diagram with delay on power off, where is the delay time on Q1 de-energization.

The other timing modes basically start from these two types of delay, whose configurations vary depending on the CLP.

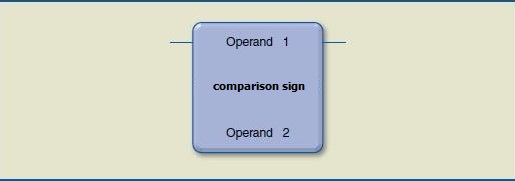

Comparison

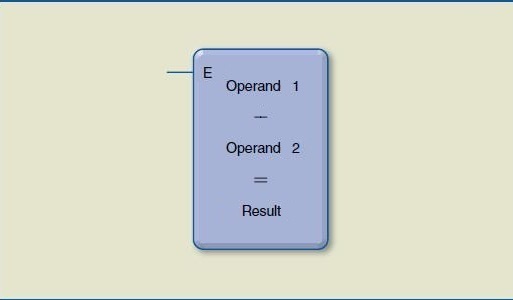

In programming, it is often necessary to compare two values. For this, the comparison instructions can be used. The comparators use two operands, which can be byte, word or constant. The program is carried out with operands 1 and 2 (image below). If the values meet the comparison condition and the comparator input is enabled, the comparator output will be activated, thus enabling the system output.

The comparisons that can be made are: equal, greater than, less than, greater than or equal to, less than or equal to and different.

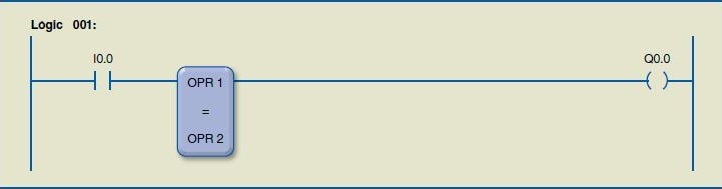

Equal to (=)

The following image shows the comparison instruction equal to (=) in Ladder diagram.

In this example, when input I0.0 is enabled, we will have the comparison between operand 1 and operand 2. If they are equal, the result will be a logical level "1" the output will be activated. If they are different, the result will be logical level "0" and the output will turn off.

Greater than (>)

The following image shows the instruction program greater than (>) in Ladder diagram.

In this example, when input I0.0 is enabled, it will have the comparison between operand 1 and operand 2. If operand 1 is greater than operand 2, the result will have logic level "1" and the output will be activated. If operand 1 is less than operand 2, the result will have logic level "0" and the output will be turned off.

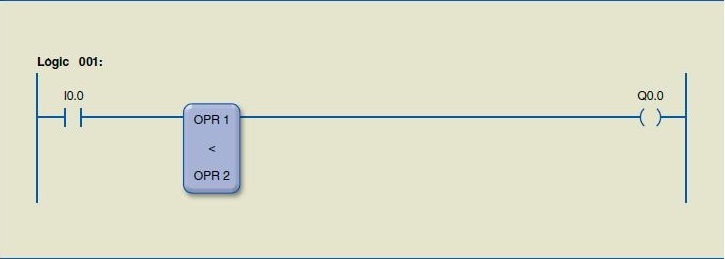

Less than (<)

The following image shows the less than instruction program that (<) in Ladder diagram.

In this example, when input I0.0 is enabled, it will have the comparison between operand 1 and operand 2. If operand 1 is smaller than operand 2, the result will have logic level "1" and the output will be activated. If operand 1 is greater than or equal to it, operating 2, the result will have logic level "0" and the output will be turned off.

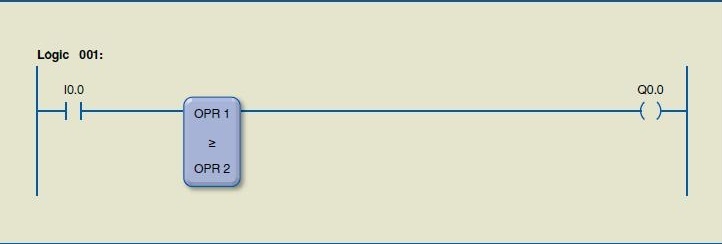

Greater or equal to (≥)

The following image shows the instruction program greater than or equal to (≥) in Ladder diagram.

In this example, when input I0.0 is enabled, it will have the comparison between operand 1 and operand 2. If operand 1 is greater than or equal to operand 2, the result will have a logical level "1" and the output will be will activate. If operand 1 is smaller than operand 2, the result will have a logical level "0" and the output will be turned off.

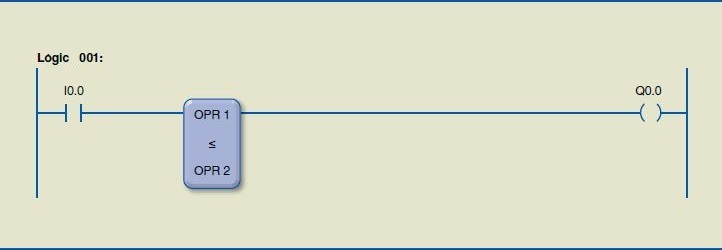

Less than or equal to (≤)

The following image shows the instruction program less than or equal to (≤) in Ladder diagram.

In this example, when input I0.0 is enabled, you will have the comparison between operand 1 and operand 2. If operand 1 is less than or equal to operand 2, the result will be a logical level "1" and the output will be will activate. If operand 1 is greater than operand 2, the result will be logical level "0" and the output will turn off.

Different from (≠)

The following image shows the program of the different comparison instruction (≠) in Ladder diagram.

In this example, when input I0.0 is enabled, it will have the comparison between operand 1 and operand 2. If the operands are different, the result will have a logical level "1" and the output will be activated. If operand 1 is equal to operand 2, the result will have a logical level of "0" and the output will turn off.

Mathematical operations

These instructions have the function of performing arithmetic operations between two operands, placing the result in a response operand called RES.

Sum (+)

When this instruction and enabled by means of input (E), it is executed to added operands (OPR1 + OPR2), placing the result in RES, as shown in the following image.

When the input is enabled, the sum of the two operands or constants is executed and, consequently, the value passes to a third operand. Operating 1 and operating 2 are the values that will be added. The allowed addresses are: bytes, words and constants. The result is the operand that will receive the result of the sum.

Subtraction (–)

When this instruction and enabled through input (E), the subtraction of the operands (OPR1 - OPR2) is executed, placing the result in RES, as shown in the image below.

Operating 1 is the value from which the value of the second operand will be subtracted and, consequently, the result passes to a third party operating. Operating 2 is the value that will be subtracted from the first operand. The allowed addresses are: bytes, words and constants.

The result is the operand that will receive the result of the subtraction. The allowed addresses are: bytes and words

Multiplication (Ă—)

When that instruction and enabled through the input (E), the multiplication of the operands (OPR1 Ă— OPR2) is executed, placing the result in RES, as shown in the image below.

When the input is enabled, there is the execution of the multiplication of the two operands and, consequently, the value passes to a third operand. Operating 1 and operating 2 are the values that will be multiplied. The allowed addresses are: bytes, words and constants.

The result is the operand that will receive the result of the multiplication. The allowed addresses are: bytes and words.

Division (Ă·)

When this instruction is enabled by means of input (E), division of operands (OPR1 Ă· OPR2) is performed, placing the result in RES as a image below.

When the entry is enabled, if you have the division of the division of the operands and, in consequence, the value goes to a third operating. Operating 1 and operating 2 are the values that will be divided. Allowed directions are son: bytes, words and constants.

The result is the operand that will receive the result of the division. Allowed types are: bytes and words.

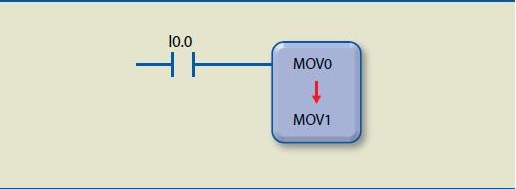

MOVE

The following image shows the special MOVE function.

This instruction has two variables: MOV0 (origin) and MOV1 (destination). When input I0.0 passes from logic level "0" to "1", the MOVE instruction is enabled, transferring the value contained in variable MOV0 (origin) to variable MOV1 (destination).